Focusing on FPGA image solution customization

FPGA simulated MIPI camera, successfully connectedNVIDIAAGX Developer

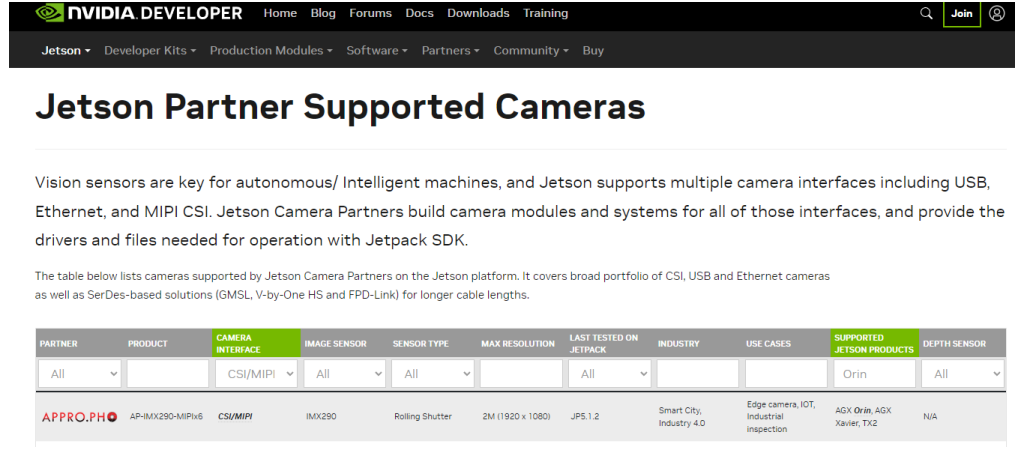

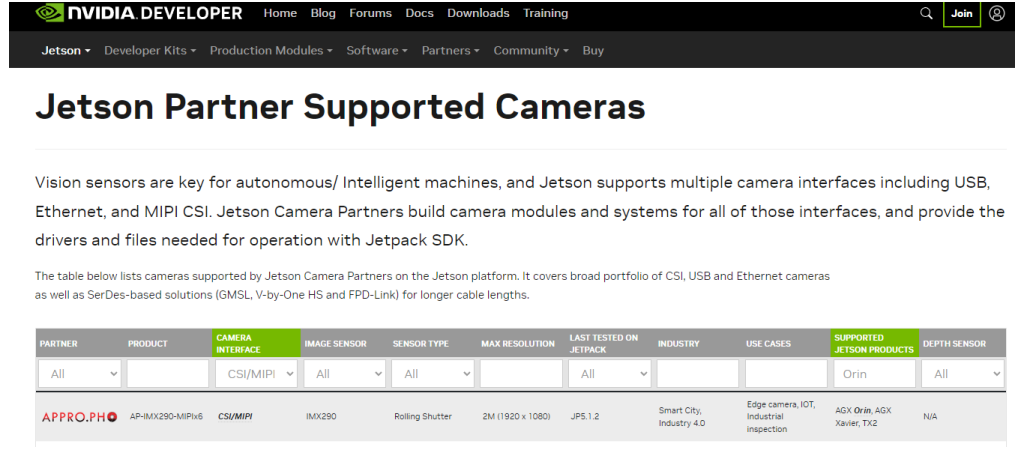

Visual cameras are key to machine intelligence/automation, and NVIDIA Jetson supports cameras from multiple partners, including cameras with USB, Ethernet, MIPI, and other interfaces. Jetson provides a complete Jetpack SDK for these cameras, enabling users to quickly connect to these cameras and implement corresponding designs.

The list of cameras supported by Jetson can be found on the official website as follows:

Select the CSI/MIPI interface and Orin suite, and the webpage will display a list of Jetson Partner supported cameras, mainly Sony's IMX290 IMX334、IMX179、IMX335、IMX415 , And Aptina's AR0234, AR0144, AR0822, etc. Therefore, for example, if users use NVIDIA's Jetson AGX Orin developer suite, the SDK of the suite natively supports CSI access to the sensors listed above, allowing users to quickly develop their own solutions.

![]()

If you choose the camera from the above list and use it with the accompanying CSI adapter board, as the Camera Partner has already pre docked with various models of NVIDIA Jetson, the driver in the original factory image is already supported by default, and can be plug and play.

howeverIf we choose a sensor model outside the list, which is not a Camera Partner product, we cannot directly use it,For example, if I want to use Sony's IMX472, IMX252, Sitewe's SC2210, SC235HGS, etc., thenIt is necessary to upgrade the supporting hardware and driver software.For this, Aoweisi provides you with a complete solution, which can be equipped with any camera or choose FPGA integrated ISP.

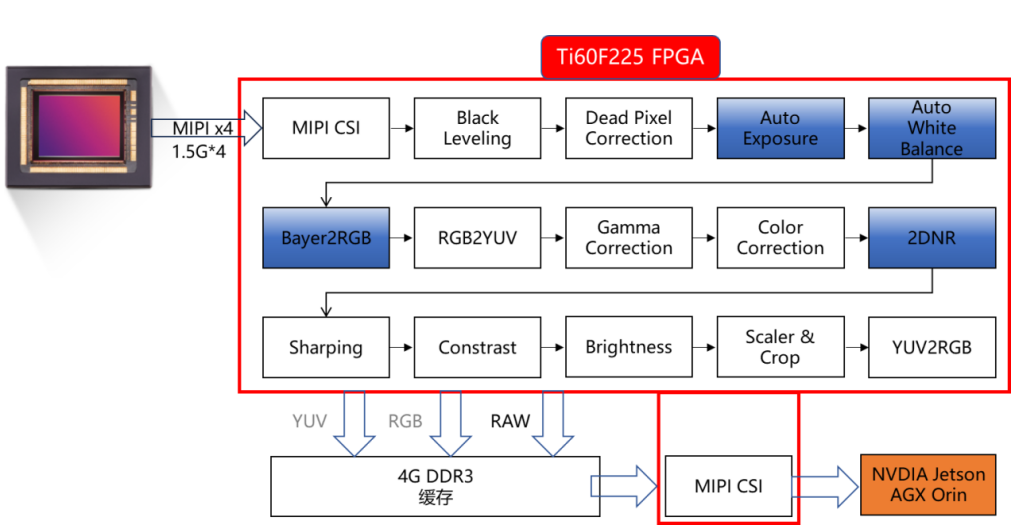

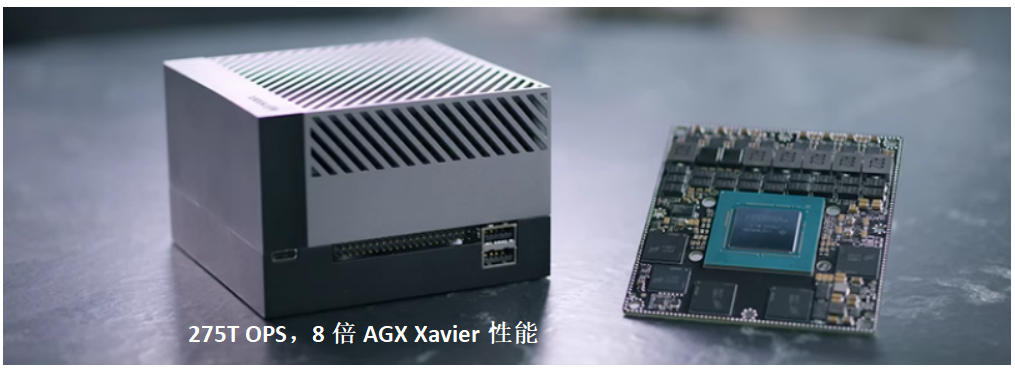

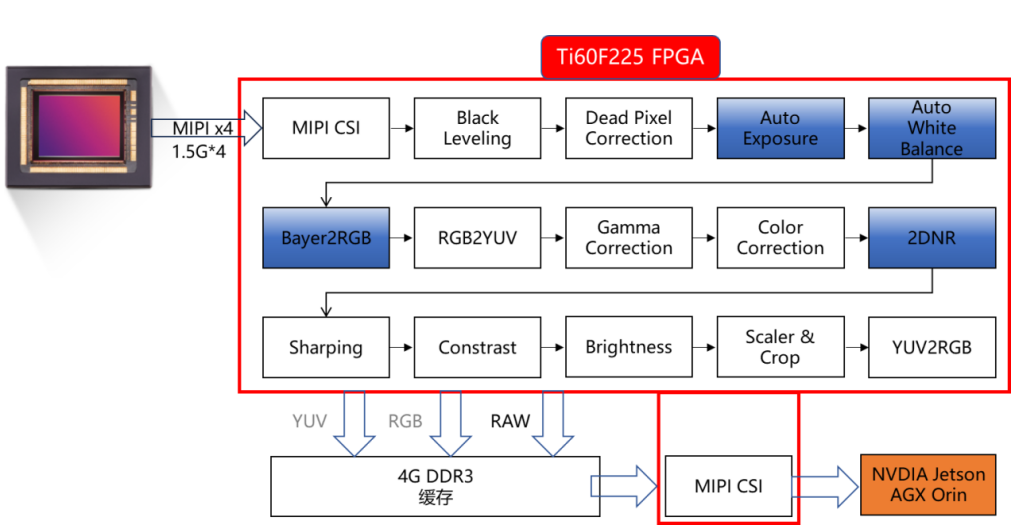

As shown in the following figure: The scheme adopts Yilingsi Titanium 16nm FPGA Ti60F225, collects image sensor data through MIPI CSI RX, undergoes a series of complex ISP operations inside the FPGA, and then sends the image data to the backend through MIPI CSI TX.

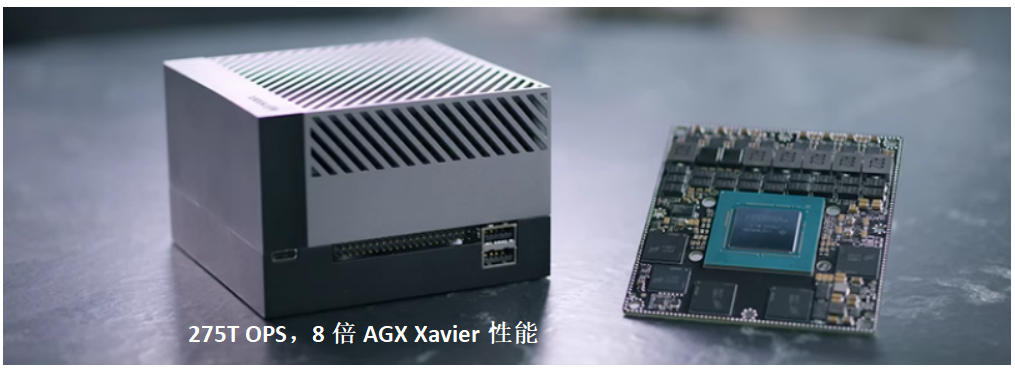

Among them, VC-MIPI-AGX is the MIPI access sub card of the NVIDIA Jetson AGX Orin developer kit developed by Aoweisi. As shown in the figure below, it is the MIPI card slot of AGX and the access sub card we designed. We use a high-speed and stable TypeC 3.0 data cable to transmit MIPI signals. The current solution can support 2 MIPI CSI channels, with a maximum bandwidth of 6Gbps per channel. At present, the solution has been successfully integrated into AGX, stable and reliable, and the baking machine has passed the test.

The low power consumption, high bandwidth, and small size characteristics of the Yilingsi 16nm titanium series FPGA fully empower terminal products to make them innovative and competitive. The titanium series Ti60 can support multi camera input, multi type screen driver, high-performance RISC-V soft core and other functions with MIPI/LVDS interfaces, suitable for various camera and sensor systems and other scene applications.

Therefore, we chose Yilingsi's FPGA as the main controller, fully utilizing its high-speed and low-power characteristics to complete the collection of MIPI CSI, ISP image processing, and transmission of MIPI CSI. The MIPI PHY of Yilingsi Ti60 FPGA is 1.5Gbps single channel, and 4 lanes support 6Gbps. At 85% effective bandwidth, the effective transmission resolution/frame rate is evaluated as follows:

|

RGB888 transmission |

Effective bandwidth |

Actual bandwidth (85%) |

result |

|

RGB888 24bit transmission |

|||

|

1920* 1080@60 |

Effective bandwidth=1920 * 1080 * 8bit * 60 * 3=2.986Gbps |

3.513Gbps |

√ |

|

1920* 1080@100 |

Effective bandwidth=1920 * 1080 * 8bit * 100 * 3=5.286Gbps |

6.219Gbps |

X |

|

1920* 1080@120 |

Effective bandwidth=1920 * 1080 * 8bit * 120 * 3=5.972Gbps |

7.026Gbps |

X |

|

Bayer 8-bit transmission |

|||

|

1920* 1080@60 |

Effective bandwidth=1920 * 1080 * 8bit * 60=0.9953Gbps |

1.171Gbps |

√ |

|

1920* 1080@100 |

Effective bandwidth=1920 * 1080 * 8bit * 100=1.659Gbps |

1.952Gbps |

√ |

|

1920* 1080@120 |

Effective bandwidth=1920 * 1080 * 8bit * 120=1.991Gbps |

2.342Gbps |

√ |

|

4096* 2304@60 |

Effective bandwidth=1920 * 1080 * 8bit * 60=4.530Gbps |

5.330Gbps |

√ |

Adopting RGB888 or Bayer 8-bit transmission has its advantages and disadvantages:

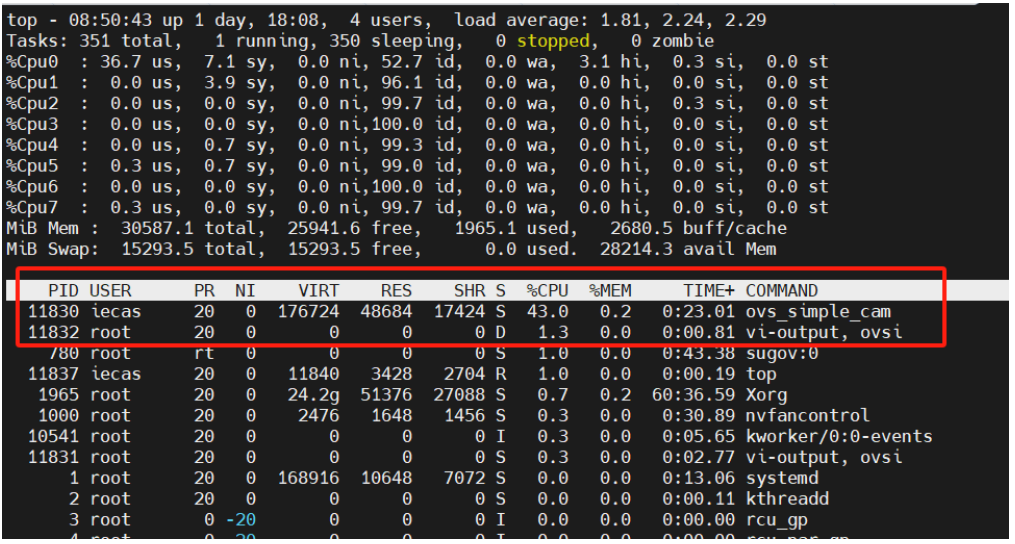

1) RGB888 8-bit transmission, AGX can directly obtain image data, with the advantage of no additional source data processing overhead; The downside is that due to Bayer's 3x bandwidth, the current FPGA scheme can only support up to 1080P60 scheme.

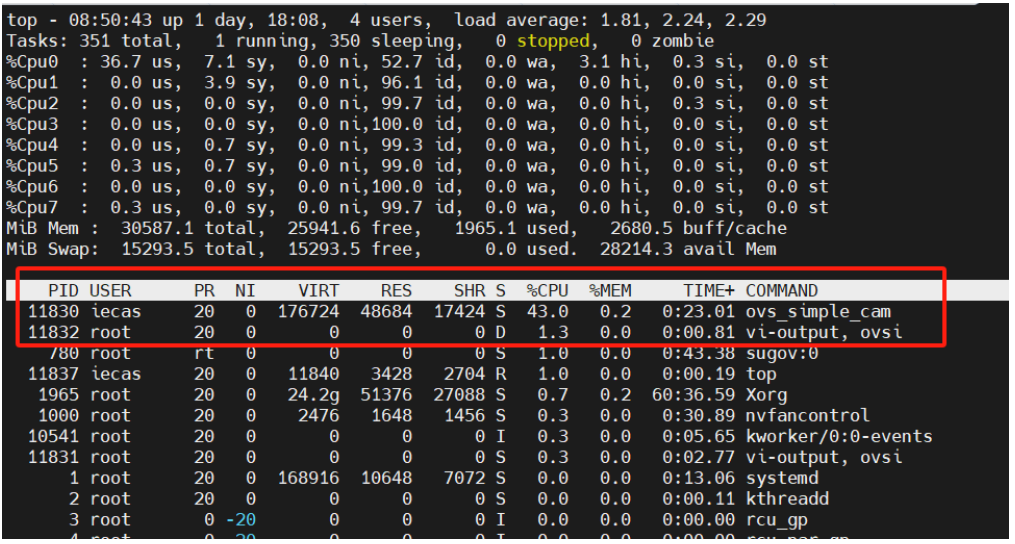

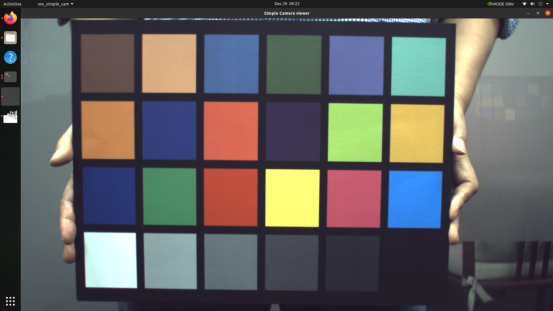

2) Bayer 8-bit transmission, with a bandwidth of 1/3 of RGB888, can support higher resolutions (4K60), and at the same resolution, can support longer transmission distances than RGB888; The shortcoming is that AGX's CPU (Neon) is needed to process the Bayer2RGB algorithm. Currently, testing 1080P120 consumes 43% of the resources of one CPU (a total of 12 CPUs, with single core resource consumption as shown in the following figure).

Based on comprehensive evaluation, due to the current use of only one AGX CPU and the user's algorithm mainly running CUDA on the GPU, the advantage of using Bayer transmission is more obvious.

NVIDIA can also perform complete ISP image processing, and even the ISP function and performance implemented by ASIC are more powerful than FPGA. However, in this solution, we have to use FPGA for complete ISP processing, mainly for the following reasons:

1) NVIDIA still requires a lot of tuning work for the selected sensors;

2) NVIDIA's ISP does not support 8-bit RAW input mode;

3) Some application engineers are not familiar with the ISP field;

4) Some ISP algorithms are not included in NVIDIA;

5) The demand for low latency requires a pipeline to complete ISP.

In view of this, we have completed a complete ISP processing process using FPGA. MIPI CSI directly outputs the data after FPGA image processing. After NVIDIA AGX receives the RGB data, users can directly carry out subsequent application algorithms. The ISP image processing pipeline based on Yilingsi FPGA is as follows:

The self-developed assembly line ISP by Aoweisi and its related features are shown in the table below:

|

parameter |

describe |

Parameter switch |

|

Black Leveling |

Black level correction |

|

|

Dead Pixel Correction |

Bad Point Correction Module (DPC) |

|

|

Auto Exposure |

Automatic exposure algorithm module |

U adjustable switch U AE brightness target value U AE sensitivity |

|

Auto White Balance |

Automatic white balance algorithm module |

|

|

Bayer2RGB |

Bayer to RGB domain |

|

|

RGB2YUV |

RGB to YUV domain |

|

|

Gamma Correction |

YUV domain Gamma correction |

U adjustable parameters |

|

Color Correction |

RGB color correction |

|

|

2DNR |

2D noise reduction algorithm module |

U adjustable switch U adjustable strength |

|

Sharping |

Edge sharpening module |

U adjustable switch U adjustable strength |

|

Saturation |

Saturation adjustment |

U adjustable strength |

|

Contrast |

Contrast enhancement module |

U adjustable strength |

|

Brightness |

Brightness adjustment module |

U adjustable strength |

|

Scaler&Crop |

Zoom/Screenshot Module |

U adjustable parameters |

|

YUV2RGB |

YUV to RGB module |

In terms of hardware, the VC-MIPI-AGX sub card designed by Ovis is used to achieve user MIPICSI to AGX Samtec input. In terms of software, it is necessary to develop specific Sensor driver adaptations based on hardware board and module design. If there are special customized control requirements, such as ISP parameter control, it is necessary to modify the Camera framework for deep customization development.

For the protection of system security, Jetson's kernel compilation was turned on when it left the factoryDriver Signature OptionsIf the newly developed driver signature certificate does not match, the driver ko file cannot be loaded. However, most users are unable to obtain the signature certificate from NVIDIA when compiling factory images, which cannot solve the ko signature problem. If you need to use a new sensor module, you will need toRecompile the kernel, generate a full system image, and burnsystemThe workload is quite enormous.

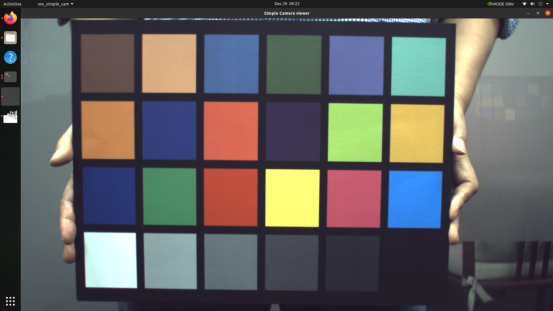

Aoweisi solves the above-mentioned software and hardware problems for customers and creatively uses typeC 3.0 cables as data transmission media, with reliable connections and stable communication. Based on the NVIDIA Jetson AGX Orin developer platform, the self-developed FPGA MIPI ISP camera connection environment is connected as follows:

Function

Programme

SZOVS,Born for FPGA images…

Buy NowDetailed introduction

FPGA模拟MIPI相机,成功接入NVIDIA AGX开发者

视觉相机是机器智能/自动化的关键,NVIDIA Jetson支持多个合作伙伴的Camera,这些相机包括USB、以太网、MIPI等接口的相机。Jetson为这些相机提供了完整的Jetpack SDK,支持用户可以快速接入这些相机,来实现相应的设计。

Jetson支持的相机列表,可以从官网中找到,如下所示:

选择CSI/MIPI接口,以及Orin套件,网页会出现Jetson Partner支持的相机列表,主要是:Sony的IMX290、IMX334、IMX179、IMX335、IMX415 ,以及Aptina的AR0234、AR0144、AR0822等。因此,比如用户使用NVIDIA的Jetson AGX Orin开发者套件,套件的SDK中就原生的支持如上列表的传感器CSI接入,用户可以快速进行自己的解决方案开发。

如果选用上述列表中的相机并搭配配套的CSI转接板,由于Camera Partner已经提前和NVIDIA Jetson各种型号做了对接,原厂镜像中驱动默认已经支持,可以做到即插即用。

但是如果我们选用了列表外的sensor型号,即非Camera Partner的产品,就无法直接使用,比如我想用Sony的IMX472、 IMX252,思特威的SC2210、SC235HGS等,则需要进行配套的硬件开和驱动软件的升级。为此,奥唯思为您提供了完整的解决方案,可搭载任意相机,也可以选FPGA集成ISP。

如下图所示:方案采用易灵思钛金16nm的FPGA Ti60F225,通过MIPI CSI RX采集图像传感器的数据,在FPGA内部经过一系列复杂的ISP运算后,再通过MIPI CSI TX将图像数据发送给后端。

其中VC-MIPI-AGX为奥唯思自研的配套NVIDIA Jetson AGX Orin开发者套件的 MIPI接入子卡。如下图所示,为AGX的MIPI卡槽,以及我们设计的接入子卡。我们使用高速稳定的TypeC 3.0数据线,来传输MIPI信号。当前方案可支持2个MIPI CSI通道,单通道最高支持6Gbps带宽。目前方案已经成功接入AGX,稳定可靠,烤机测试通过。

易灵思16nm钛金系列FPGA的低功耗、高带宽、小体积特点,充分赋能终端产品使其具有创新性和竞争力。钛金系列Ti60可支持MIPI/LVDS等接口的多摄像头输入、多类型屏幕驱动、高性能RISC-V软核等功能,适用于各种相机和传感器系统等场景应用。

因此我们选用了易灵思的FPGA作为主控,充分利用其高速低功耗的特性,完成了MIPI CSI的采集、ISP图像处理,以及MIPI CSI的发送。易灵思Ti60 FPGA的MIPI PHY为1.5Gbps单通道,4 lane支持6Gbps,在85%有效带宽下,评估有效的传输分辨/帧率,如下:

|

RGB888传输 |

有效带宽 |

实际带宽 (85%) |

结果 |

|

RGB888 24bit传输 |

|||

|

1920*1080@60 |

有效带宽= 1920*1080*8bit*60*3 = 2.986Gbps |

3.513Gbps |

√ |

|

1920*1080@100 |

有效带宽= 1920*1080*8bit*100*3 = 5.286Gbps |

6.219Gbps |

× |

|

1920*1080@120 |

有效带宽= 1920*1080*8bit*120*3 = 5.972Gbps |

7.026Gbps |

× |

|

Bayer 8bit传输 |

|||

|

1920*1080@60 |

有效带宽= 1920*1080*8bit*60 = 0.9953Gbps |

1.171Gbps |

√ |

|

1920*1080@100 |

有效带宽= 1920*1080*8bit*100= 1.659Gbps |

1.952Gbps |

√ |

|

1920*1080@120 |

有效带宽= 1920*1080*8bit*120 = 1.991Gbps |

2.342Gbps |

√ |

|

4096*2304@60 |

有效带宽= 1920*1080*8bit*60 = 4.530Gbps |

5.330Gbps |

√ |

采用RGB888或者Bayer 8bit传输,各有优缺点:

1)RGB888 8bit传输,AGX可以直接获取图像数据,好处是没有额外的源数据处理开销;坏处是由于Bayer的3倍带宽,当前FPGA方案只能支持到1080P60方案。

2)Bayer 8bit传输,带宽是RGB888的1/3,可以支持更高的分辨率(4K60),同时在同等分辨率下,比RGB888可以支持更长的传输距离;不足的是需要AGX的CPU(Neon)来处理Bayer2RGB算法,目前测试1080P120消耗了1个CPU 43%的资源(共12个CPU,单核资源消耗如下图所示)。

综合评估下,由于当前只用了AGX 1个CPU,并且用户的算法主要在GPU上跑CUDA,因此采用Bayer传输的优势更明显。

NVIDIA同样可以做完整的ISP图像处理,甚至ASIC实现的ISP功能与性能相比FPGA更强大,但在此方案中,我们不得不采用FPGA进行完整的ISP处理,主要原因如下:

1)针对选定的Sensor,NVIDIA仍需要大量的Tuning工作;

2)NVIDIA的ISP不支持8bit RAW输入模式;

3)部分应用工程师,并不熟悉ISP领域;

4)部分ISP算法,NVIDIA并没有包含;

5)低延时的需求,需要流水线完成ISP。

鉴于此,我们采用FPGA完成了一套完整的ISP处理流程,MIPI CSI直接输出经过FPGA图像处理完后的数据,NVIDIA AGX拿到RGB数据后,用户可以直接进行后续的应用算法。基于易灵思FPGA的ISP图像处理Pipeline,如下所示:

奥唯思自研的流水线ISP,相关的Feature,如下表所示:

|

参数 |

描述 |

参数开关 |

|

Black Leveling |

黑电平矫正 |

|

|

Dead Pixel Correction |

坏点矫正模块(DPC) |

|

|

Auto Exposure |

自动曝光算法模块 |

u 可调开关 u AE亮度目标值 u AE灵敏度 |

|

Auto White Balance |

自动白平衡算法模块 |

|

|

Bayer2RGB |

Bayer转RGB域 |

|

|

RGB2YUV |

RGB转YUV域 |

|

|

Gamma Correction |

YUV域Gamma矫正 |

u 可调参数 |

|

Color Correction |

RGB色彩矫正 |

|

|

2DNR |

2D降噪算法模块 |

u 可调开关 u 可调强度 |

|

Sharping |

边缘锐化模块 |

u 可调开关 u 可调强度 |

|

Saturation |

饱和度调节 |

u 可调强度 |

|

Contrast |

对比度增强模块 |

u 可调强度 |

|

Brightness |

亮度调节模块 |

u 可调强度 |

|

Scaler&Crop |

缩放/截屏模块 |

u 可调参数 |

|

YUV2RGB |

YUV转RGB模块 |

硬件方面,采用奥唯思设计的VC-MIPI-AGX子卡,实现了用户MIPICSI转AGX Samtec的输入。软件方面,则需要根据硬件板卡和模组设计,开发特定的Sensor驱动适配。如果有特殊定制的控制需求,比如ISP参数的控制,则需要修改Camera框架,进行深度定制开发。

出于对系统安全性的保护,Jetson出厂时的,内核编译打开了驱动签名选项,如果新开发的驱动签名证书不匹配,则驱动ko文件无法加载。但是一般用户无法拿到NVIDIA编译出厂镜像时的签名证书,无法解决ko签名问题。如果需要使用新的sensor模组,则需要重新编译内核、生成全系统镜像、烧录系统,工作量相当巨大。

奥唯思为客户解决上述软硬件难题,并创造性地使用typeC 3.0线缆作为数据传输介质,连接可靠,通信稳定。基于NVIDIA Jetson AGX Orin开发者平台,接入的自研的FPGA MIPI ISP相机连接环境,如下所示:

302, Building 17, Nanshan Ruiyuan, Xili Longzhu 3rd Road, Nanshan District, Shenzhen City, Guangdong Province

302, Building 17, Nanshan Ruiyuan, Xili Longzhu 3rd Road, Nanshan District, Shenzhen City, Guangdong Province

19926595670

19926595670

cb@szovs.com

cb@szovs.com

WeChat

WeChat

Skype

Skype

Official WeChat

Official WeChat

website

FPGA website

Official account

Official WeChat public account

Official account

Official account

Skype

Skype

Mailbox

cb@szovs.com

Comeback